一文读懂PLL锁相环的基本原理及在通信链路中的重要性

2024.2.1

频率合成器是通信系统的心脏,具有不可或缺的重要地位。目前产生稳定频率的常用方法之一就是采用PLL(Phase-Locked Loop,锁相环)。PLL是一种常用的反馈系统,被广泛应用到电路和控制系统中,可以用来产生稳定的输出信号频率,对频率进行锁定和跟踪,广泛应用于无线通信、卫星通信、雷达系统、射频测试设备、频谱分析仪等领域。除了锁定特定频率外,还能实现数字信号处理、时钟生成和频率合成等功能。

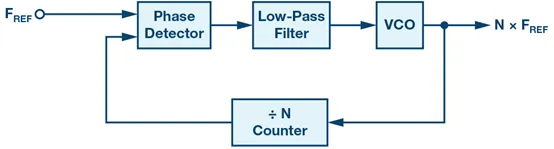

一个典型的PLL系统包含相位比较器(Phase Comparator)、环形数字控制器(Loop Filter)、振荡器(Voltage-Controlled Oscillator,VCO)和反馈网络(Feedback Network)。

- PLL的核心是一个反馈环路,通过不断比较输入信号和反馈信号的相位差来调整输出信号的频率,使其与输入信号同步

- 相位比较器接收输入信号和反馈信号,并产生一个误差信号,表示两者之间的相位差

- 环形数字控制器接收相位比较器的误差信号,并根据这个误差信号来调节振荡器的控制电压

- 当控制电压增加时,输出频率也相应增加;当控制电压减小时,输出频率也减小。通过不断调整振荡器的频率,PLL系统可以迅速跟踪输入信号的频率变化,并在稳定状态下与输入信号保持同步

- 同时反馈网络将振荡器的输出信号反馈到相位比较器,与输入信号进行比较

如此一来,系统就能通过不断调整振荡器的频率来使输入信号和输出信号保持同步

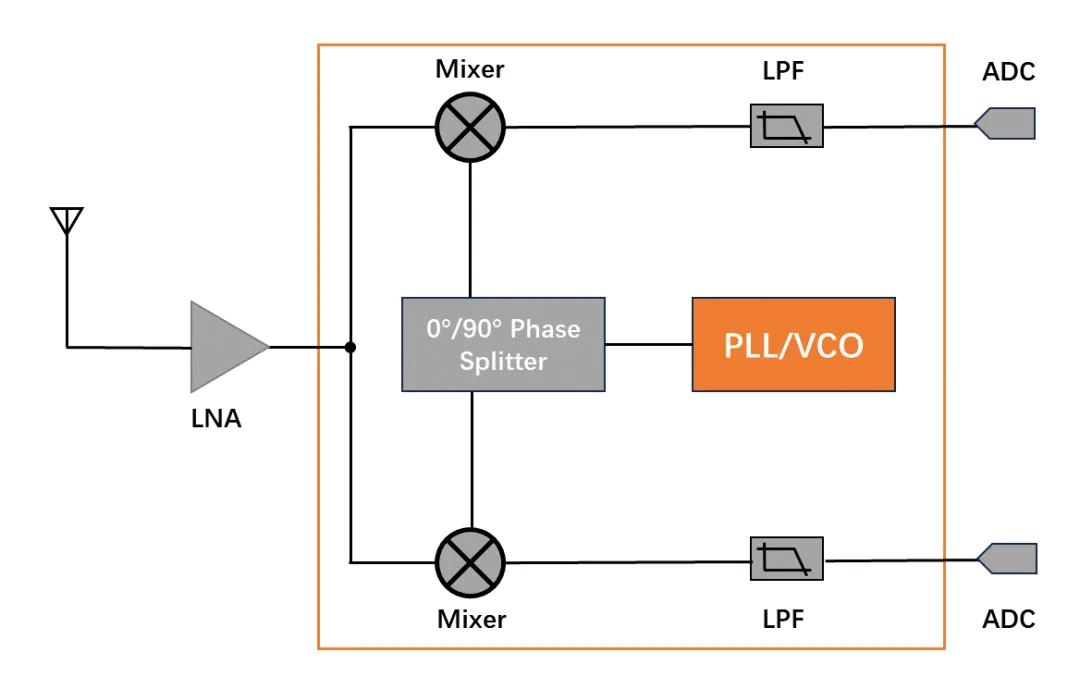

在通信链路中,PLL通过以下的多种功能得以保证数据的可靠传输和系统的正常运行:

1、生成稳定的高频率信号和系统中的时钟信号

2、将多个频带信号合成为一个宽带信号,这在通信和射频领域中尤其重要

3、从接收的数据流中提取时钟信号,保证数据的正确采样

4、能抑制抖动,产生稳定的本振信号,从而提高数据传输的可靠性,并确保各个系统元件的同步操作

如今,PLL锁相环已经成为众多电子产品的基本组成部分。从小型存储芯片到超级计算机都有其用武之地。根据调研机构报告,到2030年,预计将创造超41亿美元的市场规模。而PLL锁相环时钟发生器市场将从在2022年的63亿美元,到2032年达到112亿美元,市场前景备受看好。

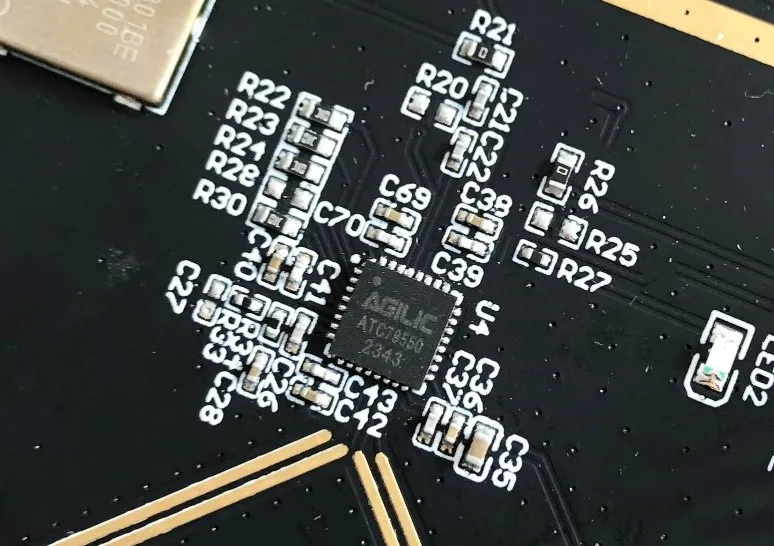

芯灵通科技的锁相环频率源产品ATC79550为我司自主研发集成PLL锁相环与VCO的宽带频率合成器,可广泛应用于需要高性能时钟源的系统中。

集成VCO的PLL

高度集成相位锁定环(PLL)、频率控制、VCO和输出分频器等功能,在一个采用5×5mm QFN封装的芯片上实现整个频率合成系统,简化了设计和布局,降低复杂性从而提高可靠性,在对尺寸要求日益严格的集成电路设计中,具有突出优势。在显著减小器件面积和电路复杂度的同时,器件性能仍然达到最优解。

频率覆盖广

频率覆盖范围为186.8 MHz – 4400 MHz,其中基波输出范围为2990 MHz – 4400 MHz,通过可编程的1/2/4/8/16分频输出。配合软件系统,可实现一键切换输出频率,方便快捷。

良好的相噪和杂散性能

在减小器件面积后,相位噪声和杂散发射的性能指标尤其重要。

ATC79550的相位噪声和杂散发射性能较为优异:PFD频率引起的杂散信号为-70 dBc;在3180 MHz载波下,10 MHz偏移时,PLL相位噪声性能可以达到-136.57 dBc/Hz。这使其可以在信号系统中保持很好的稳定性,提高频谱纯度,可用于射频接收机与发射机。

芯灵通科技的ATC79550是一款性能优异、灵活多样、易于集成和控制的频率合成器,适用于各种射频和通信应用中。

目前已有成熟产品,欢迎广大通信系统应用商垂询获取更多信息。